A win, sort of, but I’ll take it

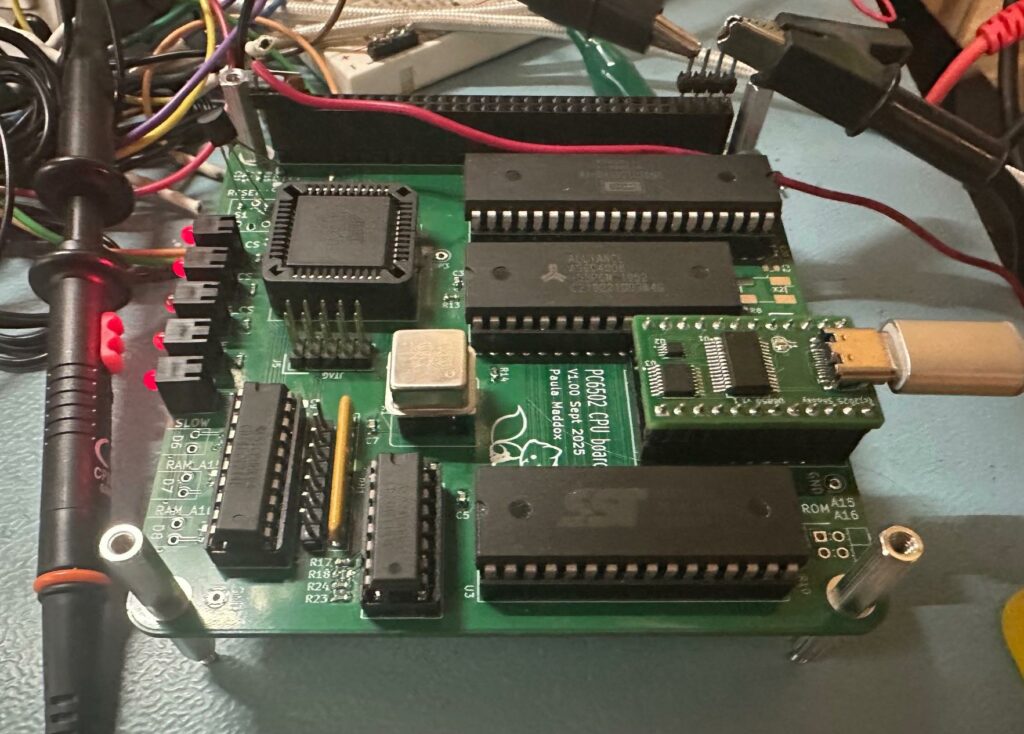

Well the PCBs arrived and I decided to build up the CPU one slowly, not building the full thing. I’m glad I didn’t.

Eventually after a lot of messing around with CPLD and ROM code I got something booting, it’s the Grant Searle ROM, but it worked. The sticking point seems to be serial comms.

After much digging I discovered that the data on the data bus isn’t valid until 25nS after the clock edge, not a problem for older chips, but for the FT245 I’m using for the serial port it’s a problem. So after delaying the clock for the write a little I got some progress.

So there are a few bodge wires (underside) and a cut track or two. But, it does seem to work with a 4MHz crystal and the CPU running at half that, 2MHz. So it works, but for a 14MHz CPU, it’s not great.

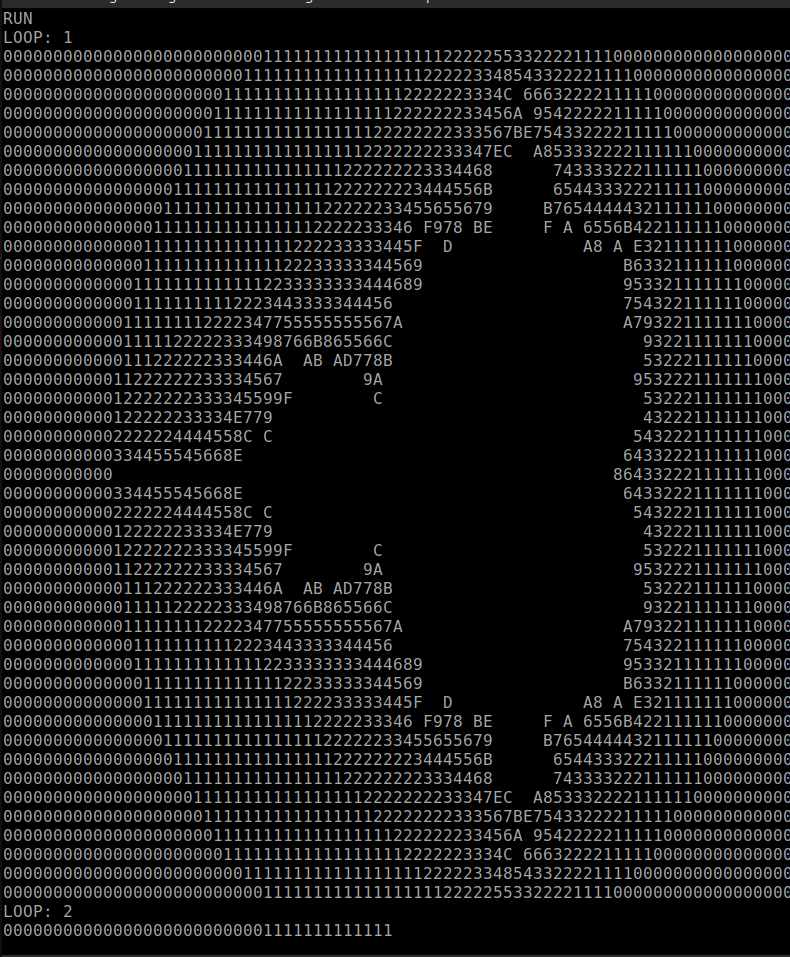

Here is a basic Mandlebrot output (0 to F or blank).

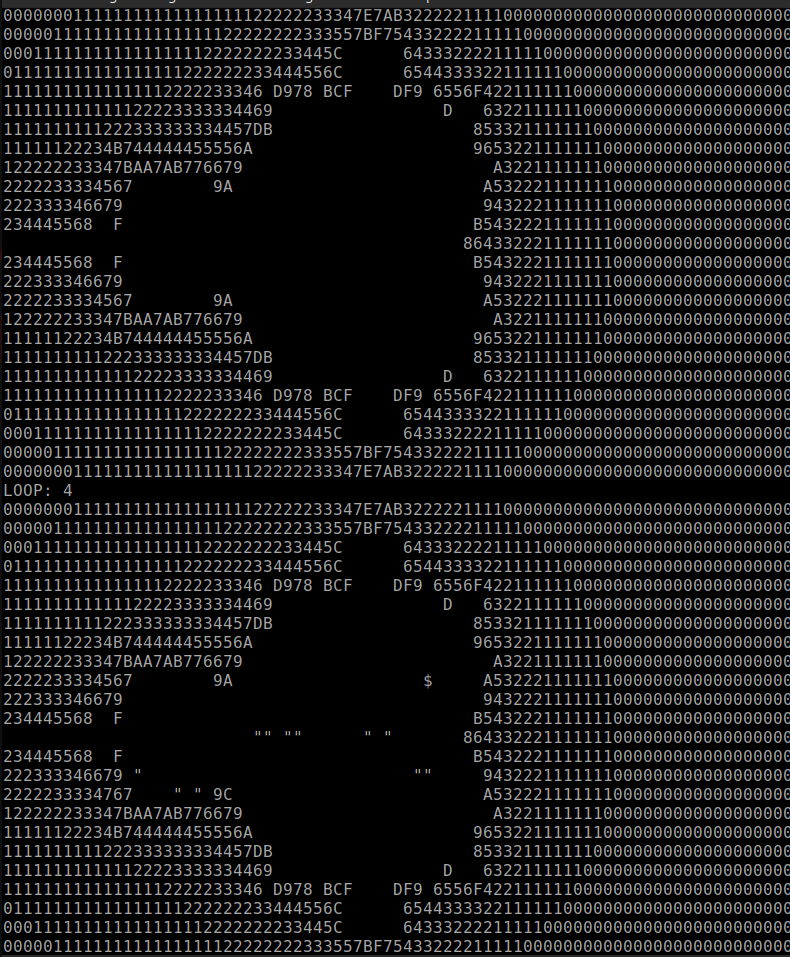

However, it isn’t always consistent or stable. So I’ve made a new version of the PCB, this time I’ve brought the FTDI control pins direct to the CPLD, and I’ve done away with the discrete clock stretcher, again bringing the pins to the CPLD. This means I should be able to more precisely control the timing, and critically be able to make changes/tweaks to improve it.

Here is an example of the corruption on the serial terminal, it seems to only be on the serial terminal, but as I can’t run it fast yet I don’t know if there are other timing issues yet.

You can see the ” and $ where there should be a space.

Hopefully the next version will resolve this. You can find the files in my GitHub, but I take no responsibility for you losing your sanity trying to make this work.